|

Xilinx FPGA Edit Page1 回首頁

|

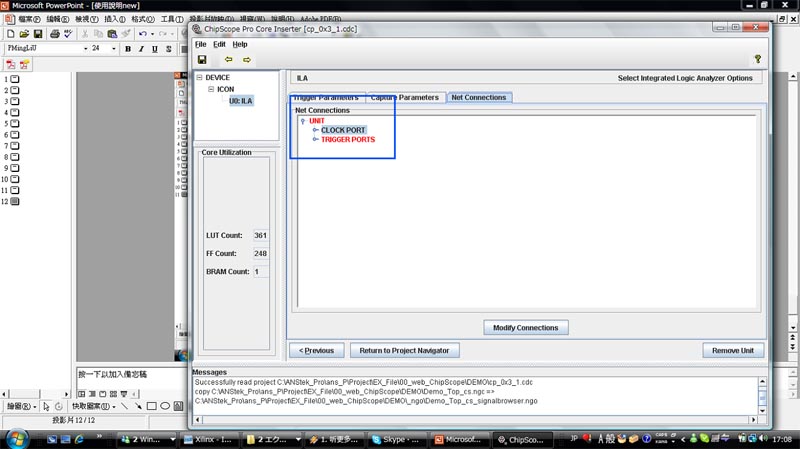

歩驟(11)

點選Net Connection會出現 Clock Port/Trigger Ports的選項 紅色表示沒有作好設定

|

|

|

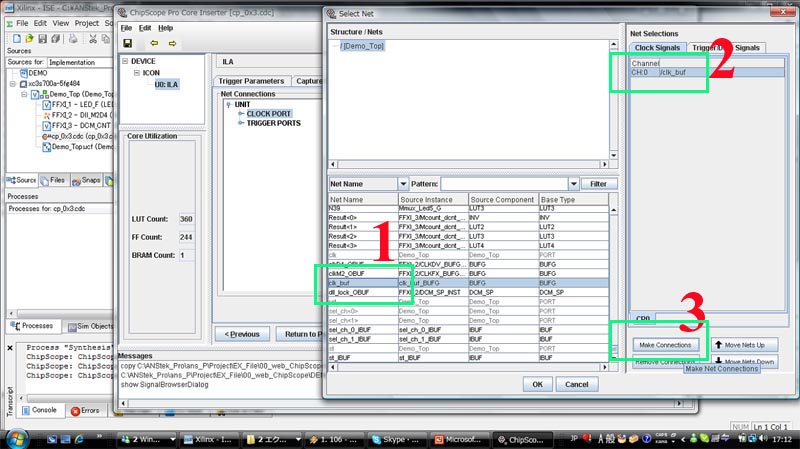

歩驟(12)

按圖示中的設定將Clock Port連接到Source Code中的Net |

|

|

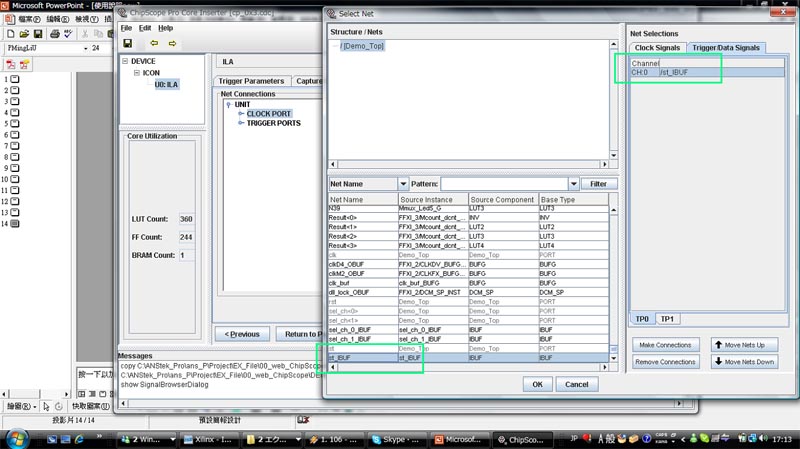

歩驟(13)

設定Trigger/ Data Port的連結,因為當初設定有兩個Port,所以可幾看見TP0與TP1選項,依序設定好

|

|

|

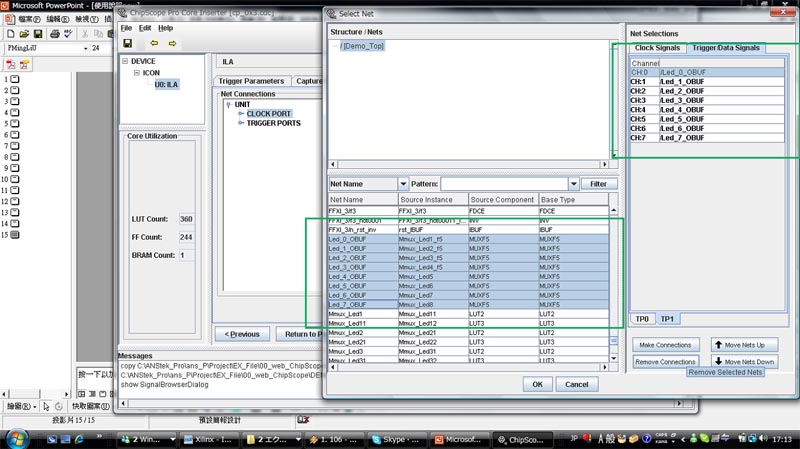

歩驟(14)

如上個步驟~

|

|

|

歩驟(15)

這是設定資料深度的選項,視使用者需求設定

|

|

|

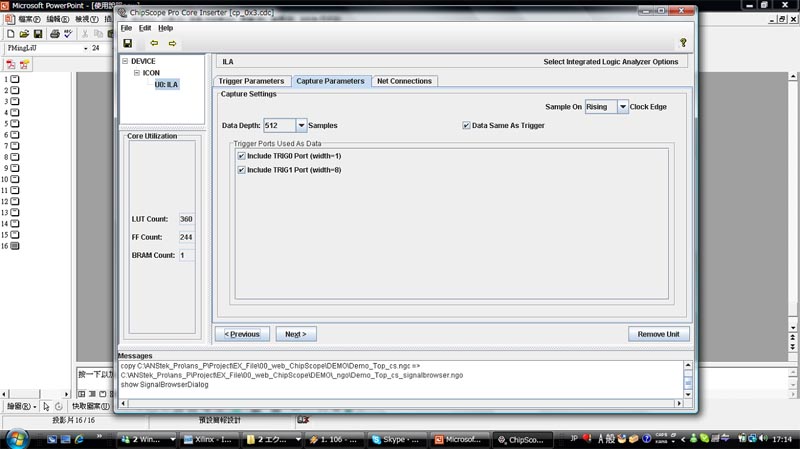

歩驟(16)

內容設定好的畫面,點選細項會出現相關資訊

|

|

|

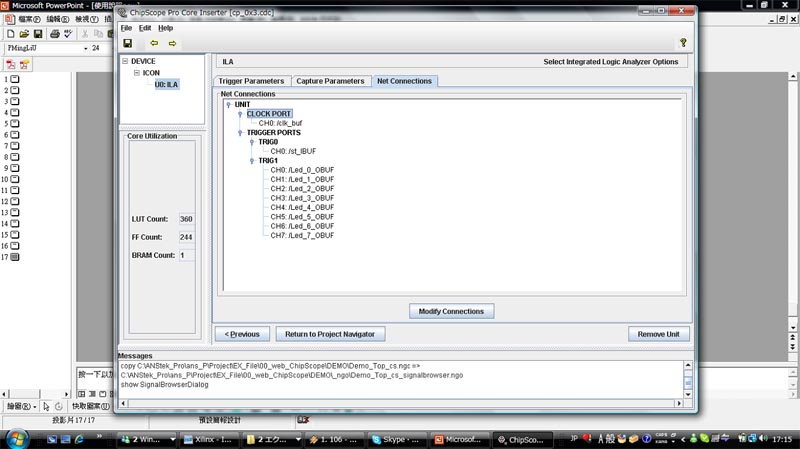

歩驟(17)

好囉〜 到了這裡可以說已經完成一半了,回到 ISE Navigator的畫面,點選Processes視窗中的最下面選項【Anlyze Design Using Chipscope】 這時候ISE會重新作Synthesize >> Implement Design >> Generate Programming File

|

|

|

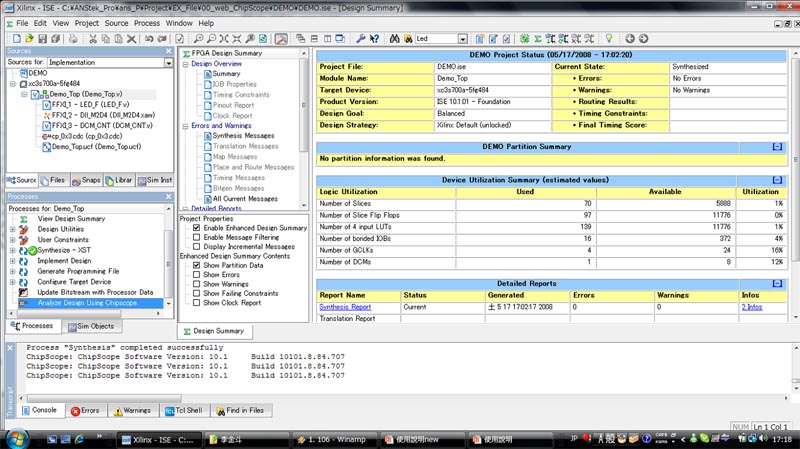

歩驟(18)

出現了ChipScope的畫面了~

|

|

|

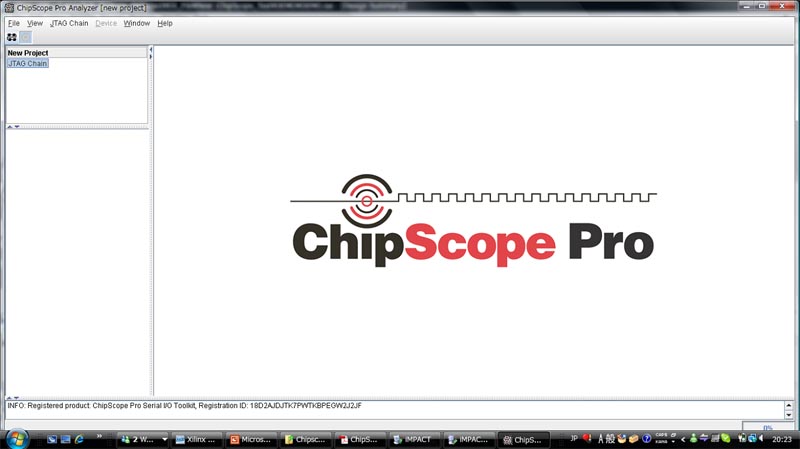

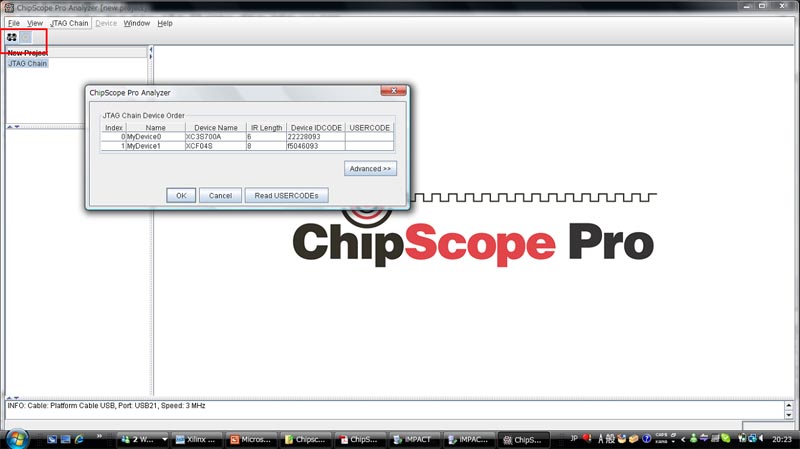

歩驟(19)

會自動出現連結的視窗〜檢視一下出現的Drvice與PCB硬體上的是否一致 . |

|

|

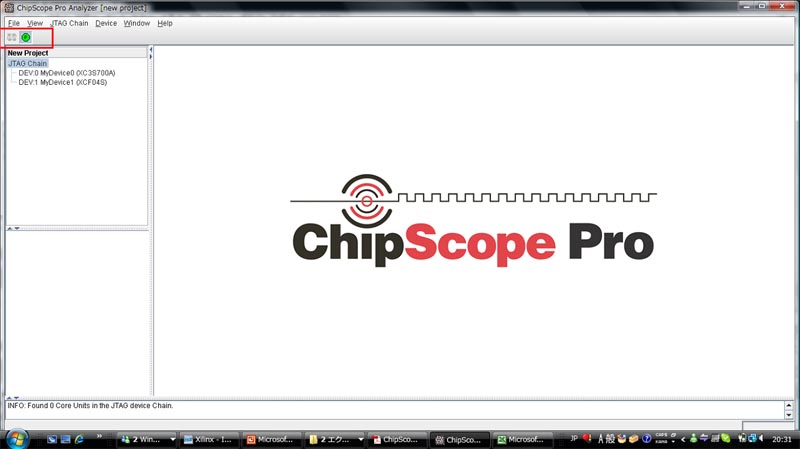

歩驟(20) 如果JTEG連接正常的話,會出現與上面圖示一樣的畫面 |