|

Xilinx 《 iMPACT Program FPGA & ROM 》 >> 回主選單 <<

|

|

iMPACT

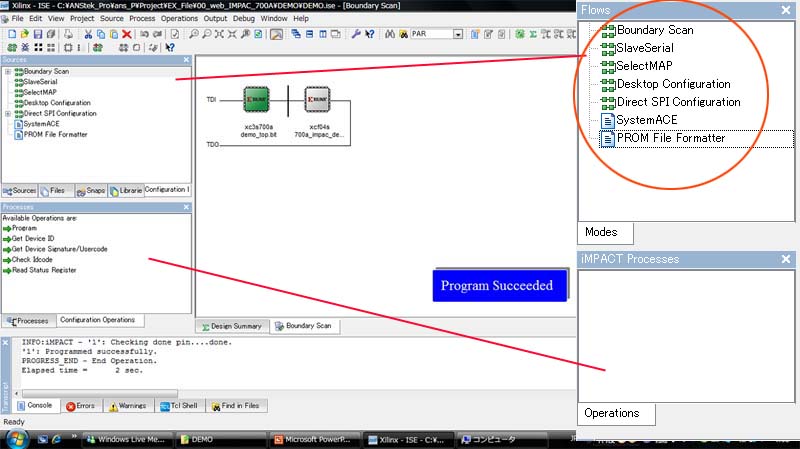

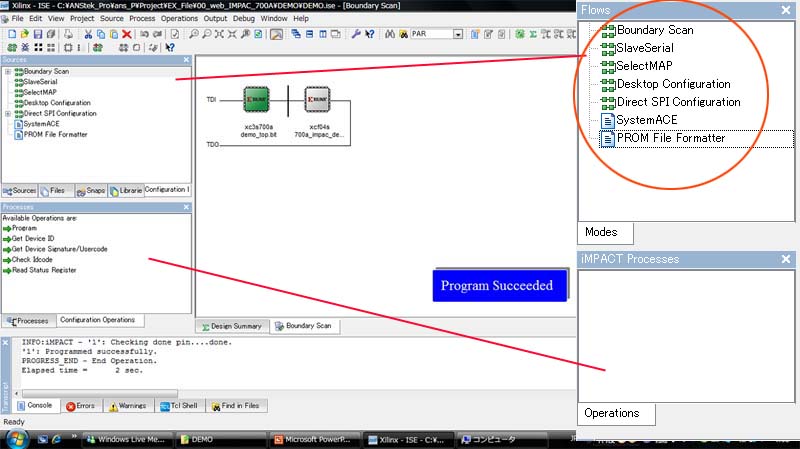

● iMPACT 是一套搭配 XILINX ISE 開發軟體內建的燒錄 CPLD/FPGA 的軟體 ● 進入主畫面時會有兩個主要視窗分別是 【 Flows 】 , 【 iMPACT Processes 】 ● 這兩個視窗與ISE中的 【 Source 】 , 【 Processes 】一樣,都有對應的關係

|

|

|

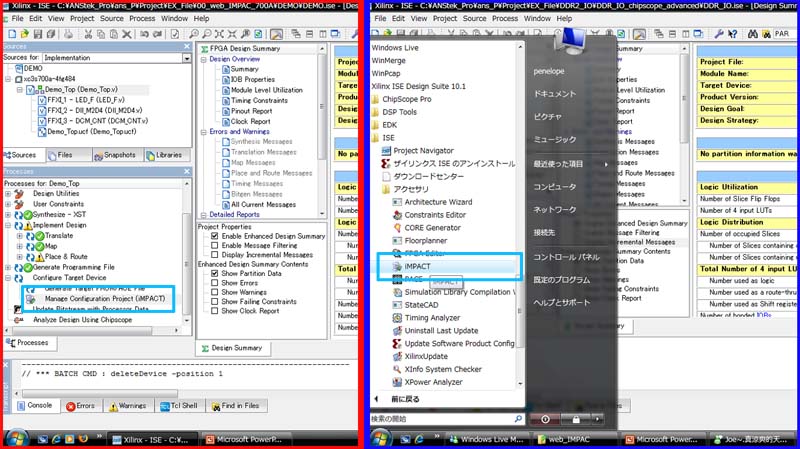

如何開啟 iMPACT ● 可透過ISE的軟體打開.一般它的選項都Implement Design下面 ● 另外也可以利用程式集中的清單在ISE的安裝目錄下找到這個選項(如圖示)

|

|

|

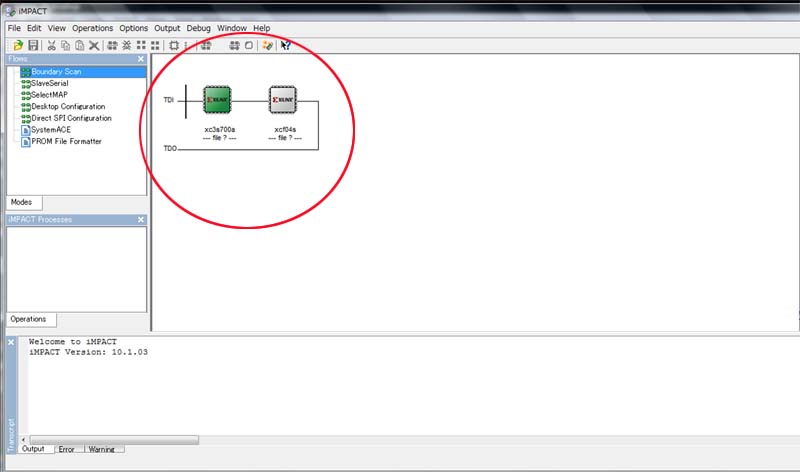

歩驟(1)

● 打開iMPACT後程式會自動執行 Boundary Scan ,如果目前硬體都已經準備好的情況下,會顯示JTEG Chain上所有的Device ● 如果是單獨開啟iMPACT,會有一個視窗詢問是不是要載入Project.....這時你可以選擇略過或是指定Project路徑

|

|

|

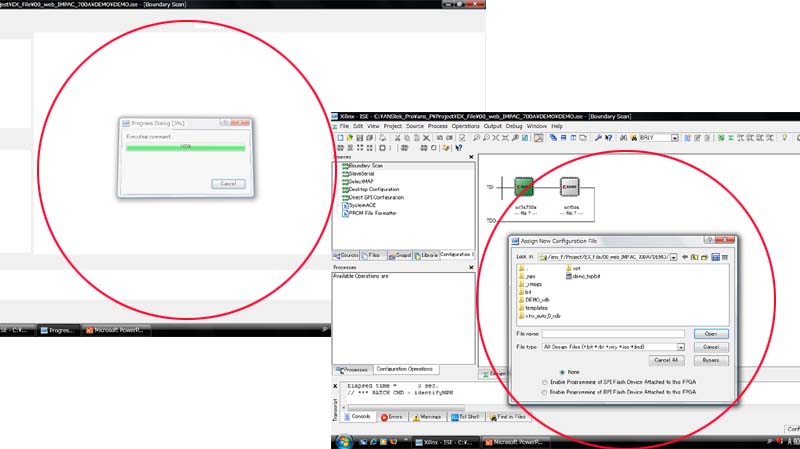

歩驟(2)

● 第一次開啟時,如果硬體都已經裝置好( 像電源,Cable之類的.... )會顯示類似上面圖示的畫面

|

|

|

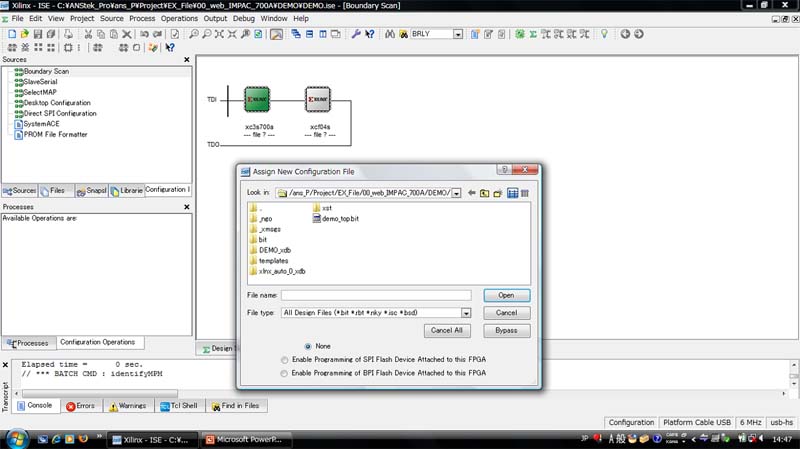

歩驟(3)

● 接著會要你選擇檔案 ● FPGA << 會需要BIT檔..燒錄後會重新RESET,關電後CODE就不存在了就是SRAM ● CPLD << 會需要JED檔,燒錄後關電還會存在 ● Xilinx PROM & SPI Flash << 這個需要MCS檔案 ?? 如何製作MCS檔案

◎ XILINX PROM 的mcs檔案不支援XILINX 3rd SPI Flash的mcs檔案

|

|

|

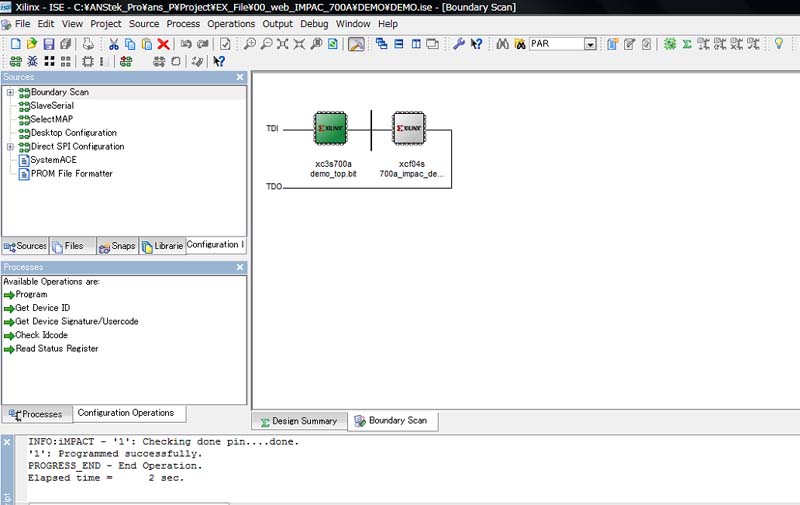

歩驟(4)

● 當選擇視窗結束後..會出現這個對應的畫面

|

|

|

歩驟(5)

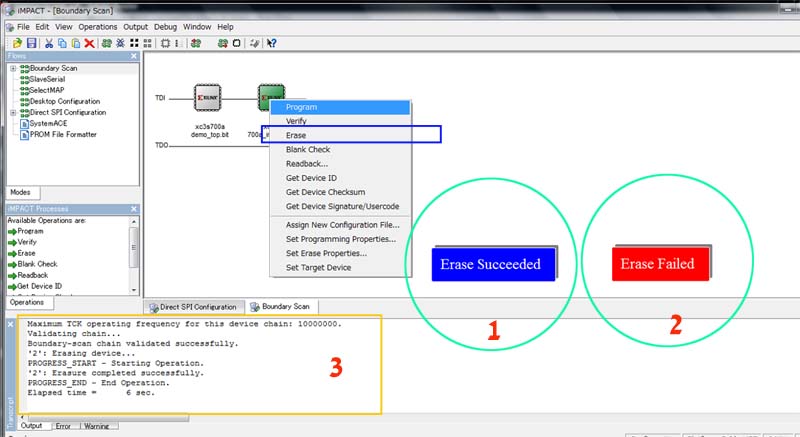

● 用滑鼠點一下Device,會出現功能視窗,我們常用的指令如下 1. Program 2. Erase

|

|

|

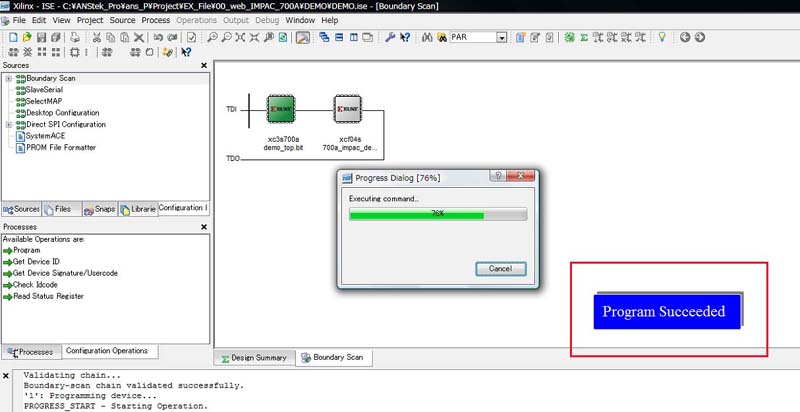

歩驟(6)

● 執行任何指令..如果成功會告訴你完成.....如果...沒成功就會顯示下圖的範例 .

|

|

|

歩驟(7)

如圖示 < 1 >表示執行的指令成功 < 2 >表示沒成功....這時可以CHECK Console <3> 的視窗.看哪個地方出了問題.....

|

|

---- § iMPACT Program FPGA & ROM ---- ---- § Generate PROM MCS File ---- ---- § Generate 3rd SPI MCS File ---- ---- § iMPACT Program 3rd SPI Flash ---- ---- § FPGA Program SPI Flash ----

|